# SRAM Memory Compiler

University of California, Santa Cruz - VLSI-DA Chasen Peters - Matthew Guthaus - Seokjoong Kim - Marcelo Siero

### Motivation

- Give system level designers access to multiple layers of abstraction for a given memory array.

- Allow for better characterization of memory before it is fabricated on the chip.

- Give designers access to an open source development tool.

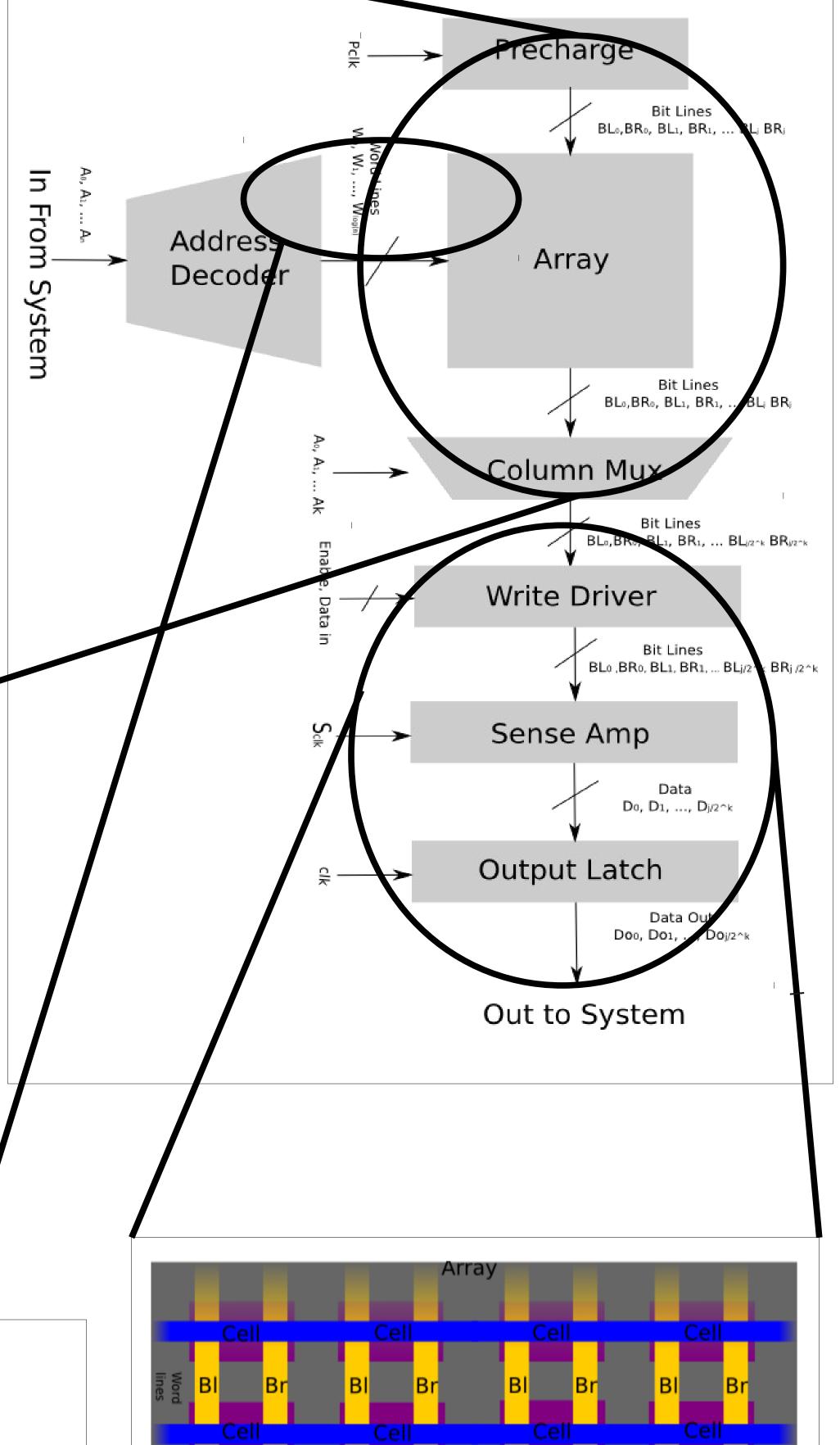

### How it Works

- Program takes in 3 parameters: Total size,

word size, and memory name.

- The program determines layout necessary for the array as close to square as possible; in other words how many words per row.

- The program then tiles the bit cells out to form the rows and columns of the array

- The compiler then tiles out the peripheral hardware for the memory to function.

- •Lastly, just like the above, the compiler constructs a spice net-list for front end simulation with estimated parasitics.

### Current Work

## LVS Checking

Once design is LVS clean, the design can be run through back annotation and the parasitics can be extracted from the design. This allows the user to run back end simulation to better characterize memory.

### Automated Timing Specs

Once the array has been constructed, this tool would then be able to find proper timing parameters for running the memory.

### Variability

Predict how the memory will behave after process variation has been accounted for and how the memory will behave under environmental noise.

# Recell Brown System In From S

# Future Work

Array

- Reliability through redundant columns and rows

- Support of many different memories besides the standard 6 transistor SRAM.

Acknowledgments

I would like to thank NSF and UC Santa Cruz for the funding and support necessary for me to work on this project. In addition I would like to say thanks to Professor Matthew Guthaus for giving me the opportunity to work on this project. Last but not least I would like to say thanks to Seokjoong Kim and Marcelo Siero for their constant guidance during my time on this project

Enable

Sense

Amp

Output Latch

Sense

Amp

Output Latch